# Simulink® HDL Coder Release Notes

# **Contents**

| Summary by Version                           | 1 |

|----------------------------------------------|---|

| Version 1.1 (R2007a) Simulink HDL Coder      | 3 |

| Version 1.0 (R2006b) Simulink HDL Coder      | 6 |

| Compatibility Summary for Simulink HDL Coder | g |

## **Summary by Version**

This table provides quick access to what's new in each version. For clarification, see "About Release Notes" on page 1.

| Version<br>(Release)            | New Features<br>and Changes | Version<br>Compatibility<br>Considerations | Fixed Bugs<br>and Known<br>Problems | Related<br>Documentation<br>at Web Site                             |

|---------------------------------|-----------------------------|--------------------------------------------|-------------------------------------|---------------------------------------------------------------------|

| Latest Version<br>V1.1 (R2007a) | Yes<br>Details              | Not applicable                             | Bug Reports                         | Printable Release<br>Notes: PDF<br>Current product<br>documentation |

| V1.0<br>(R2006b)                | Yes<br>Details              | Not applicable                             | Bug Reports                         | No                                                                  |

### **About Release Notes**

Use release notes when upgrading to a newer version to learn about new features and changes, and the potential impact on your existing files and practices. Release notes are also beneficial if you use or support multiple versions.

If you are not upgrading from the most recent previous version, review release notes for all interim versions, not just for the version you are installing. For example, when upgrading from V1.0 to V1.2, review the New Features and Changes, Version Compatibility Considerations, and Bug Reports for V1.1 and V1.2.

### **New Features and Changes**

These include

- New functionality

- Changes to existing functionality

- Any version compatibility considerations associated with each new feature or change

### **Version Compatibility Considerations**

When a new feature or change introduces a known incompatibility between versions, its description includes a **Compatibility Considerations** subsection that details the impact. For a list of all new features and changes that have compatibility impact, see the "Compatibility Summary for Simulink HDL Coder" on page 9.

Compatibility issues that become known after the product has been released are added to Bug Reports at the MathWorks Web site. Because bug fixes can sometimes result in incompatibilities, also review fixed bugs in Bug Reports for any compatibility impact.

### **Fixed Bugs and Known Problems**

MathWorks Bug Reports is a user-searchable database of known problems, workarounds, and fixes. The MathWorks updates the Bug Reports database as new problems and resolutions become known, so check it as needed for the latest information.

Access Bug Reports at the MathWorks Web site using your MathWorks Account. If you are not logged in to your MathWorks Account when you link to Bug Reports, you are prompted to log in or create an account. You then can view bug fixes and known problems for R14SP2 and more recent releases.

The Bug Reports database was introduced for R14SP2 and does not include information for prior releases. You can access a list of bug fixes made in prior versions via the links in the summary table.

#### Related Documentation at Web Site

**Printable Release Notes (PDF).** You can print release notes from the PDF version, located at the MathWorks Web site. The PDF version does not support links to other documents or to the Web site, such as to Bug Reports. Use the browser-based version of release notes for access to all information.

**Product Documentation.** At the MathWorks Web site, you can access complete product documentation for the current version and some previous versions, as noted in the summary table.

## Version 1.1 (R2007a) Simulink HDL Coder

This table summarizes what's new in V1.1 (R2007a):

| New Features and<br>Changes | Version<br>Compatibility<br>Considerations | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site |

|-----------------------------|--------------------------------------------|----------------------------------|-----------------------------------------|

| Yes<br>Details below        | No                                         | Bug Reports                      | Printable Release<br>Notes: PDF         |

|                             |                                            |                                  | Current product documentation           |

New features and changes introduced in this version are

- "Sign Block Supported for HDL Code Generation" on page 3

- "Link for Cadence Incisive HDL Cosimulation Block Supported" on page 3

- "GUI Support for Generation of EDA Tool Scripts" on page 4

- "Embedded MATLAB Function Block Supported for HDL Code Generation" on page 5

- "Stateflow HDL Code Generation Updates" on page 5

## Sign Block Supported for HDL Code Generation

The Sign block (Simulink/Math Operations/Sign) is now supported for HDL code generation. See "Summary of Block Implementations" in the *Simulink HDL Coder User's Guide* for further information.

## Link for Cadence Incisive HDL Cosimulation Block Supported

Simulink HDL Coder now supports HDL code generation for the Link for Cadence® Incisive® HDL Cosimulation Block. You can use the HDL Cosimulation block with Simulink HDL Coder to generate an interface to your manually written or legacy HDL code. When an HDL Cosimulation block is included in a model, Simulink HDL Coder generates a VHDL or Verilog interface, depending on the selected target language. See "Code Generation"

for HDL Cosimulation Blocks" in the Simulink HDL Coder User's Guide for details.

## **GUI Support for Generation of EDA Tool Scripts**

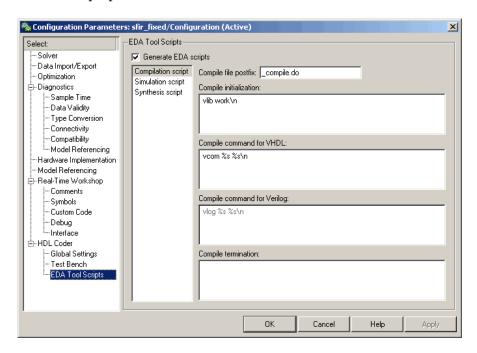

The new **EDA Tool Scripts** pane of the Simulink HDL Coder GUI (shown in the following figure) lets you set all options that control generation of script files for third-party electronic design automation (EDA) tools. In previous releases, script generation options were available only through makehdl and makehdltb properties.

The list on the left of the **EDA Tool Scripts** pane lets you select from the following categories of options:

- **Compilation script**: Options related to customizing scripts for compilation of generated VHDL or Verilog code.

- Simulation script: Options related to customizing scripts for HDL simulators.

• **Synthesis script**: Options related to customizing scripts for synthesis tools.

See "Generating Scripts for HDL Simulators and Synthesis Tools" in the *Simulink HDL Coder User's Guide* for detailed information on the **EDA Tool Scripts** options and on script generation in general.

# Embedded MATLAB Function Block Supported for HDL Code Generation

Simulink HDL Coder now supports synthesizable HDL code generation from the Embedded MATLAB Function block. See "Generating HDL Code with the Embedded MATLAB Function Block" for detailed information.

We are interested in getting your feedback on this introductory feature. Please send your responses to: hdlcoder\_feedback@mathworks.com.

## **Stateflow HDL Code Generation Updates**

This section describes some limitations on the use of Stateflow charts in HDL code generation have been removed in the current release. These are:

### **Restriction on Reading from Output Ports Removed**

In the previous release, reading from output ports was disallowed. This restriction has been relaxed. You can now read from output ports if outputs are registered. (Outputs are registered if the **Initialize Outputs Every Time Chart Wakes Up** option is deselected.)

# Stateflow HDL Code Generator Fully Supports Simulink Fixed Point Data Type

In the previous release, fixed-point data type support for Stateflow HDL code generation was limited to fixed point without scaling. This limitation has been removed. You can now use Simulink fixed-point data types without restriction in Stateflow charts intended for HDL code generation.

## Version 1.0 (R2006b) Simulink HDL Coder

This table summarizes what's new in V1.0 (R2006b):

| New Features and<br>Changes | Version Compatibility Considerations | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site |

|-----------------------------|--------------------------------------|----------------------------------|-----------------------------------------|

| Yes<br>Details below        | No                                   | Bug Reports                      | No                                      |

#### Introduction to Simulink HDL Coder

Simulink® HDL Coder lets you generate hardware description language (HDL) code based on models developed in Simulink and finite-state machines developed in Stateflow®. Simulink HDL Coder brings the Simulink Model-Based Design approach into the domain of application-specific integrated circuit (ASIC) and field programmable gate array (FPGA) development. Using Simulink HDL Coder, system architects and designers can spend more time on fine-tuning algorithms and models through rapid prototyping and experimentation and less time on HDL coding.

Simulink HDL Coder generates bit-true and cycle-accurate, synthesizable Verilog and VHDL code from Simulink models and Stateflow diagrams. The automatically generated HDL code is target independent.

You can simulate and synthesize the automatically generated HDL using industry standard tools and then map it into field-programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs). You can also use the automatically generated HDL code to verify existing HDL code using formal or functional verification tools.

Simulink HDL Coder also generates test benches, enabling rapid verification of the generated HDL code using HDL simulation tools.

Version 1.0 of Simulink HDL Coder includes these features:

Generation of synthesizble VHDL or Verilog code from Simulink models and Stateflow charts

- Code generation configured and initiated via graphical user interface,

MATLAB command line interface, or M-file programs

- Test bench generation (VHDL or Verilog) for validating generated code

- Generation of models that are bit-true and cycle-accurate with respect to generated HDL code

- Numerous options for controlling the contents and style of the generated HDL code and test bench

- Block support:

- Simulink built-in

- Signal Processing Blockset

- Link for ModelSim HDL Cosimulation block

- Stateflow chart

- User-selectable optimized block implementations provided for commonly used blocks

- Code generation control files support:

- Selection of alternate block implementations for specific blocks or sets of blocks in the model

- Setting of code generation options

- Selection of the model or subsystem from which code is to be generated.

- Definition of default or template HDL code generation settings for your organization

- Generation of subsystem-based identification comments and mapping files for easy tracing of HDL entities back to corresponding elements of the original model

- Generation of interfaces to existing HDL code via:

- Black box subsystem implementation

- Cosimulation with ModelSim HDL simulator (requires link for ModelSim)

- Compatibility checker utility that examines your model for HDL code generation compatibility, and generates HTML report with hyperlinks to problematic blocks

- Generation of scripts for EDA tools:

- ModelSim

- Synplify

- Model features supported for code generation in Version 1.0:

- Real data types only (fixed-point and double) (Complex data types are not supported.)

- Fixed-step, discrete, single-rate models

- Scalar and vector ports (row or column vectors only)

#### For More Information

See the Simulink HDL Coder User's Guide for comprehensive information on Simulink HDL Coder.

## **Compatibility Summary for Simulink HDL Coder**

This table summarizes new features and changes that might cause incompatibilities when you upgrade from an earlier version, or when you use files on multiple versions. Details are provided in the description of the new feature or change.

| Version (Release)               | New Features and Changes with Version Compatibility Impact |

|---------------------------------|------------------------------------------------------------|

| Latest Version<br>V1.1 (R2007a) | None                                                       |

| V1.0 (R2006b)                   | None                                                       |